研究人员开发基于硅光子的可扩展、可持续AI硬件技术

人工智能(AI)的兴起深刻改变了众多行业格局。在深度学习技术和大数据的推动下,AI模型的训练需要强大的算力支撑。当前AI基础设施主要依赖图形处理器(GPU),但其运行所需的高算力消耗和能源成本仍是关键挑战。构建更高效、可持续的AI基础设施将成为推动未来AI发展的重要突破口。

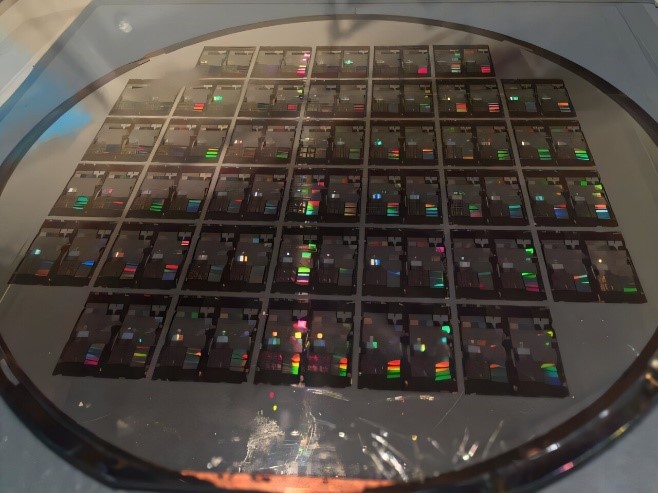

图片来源:IEEE JSTQE

据外媒报道,最近发表在期刊《IEEE Journal of Selected Topics in Quantum Electronics》的一项研究展示了一种基于光子集成电路(PIC)的新型AI加速平台。与传统的GPU架构相比,该平台具有更优异的可扩展性和能效表现。

这项研究由惠普实验室(Hewlett Packard Labs)高级研究员Bassem Tossoun博士领导,展示了采用III-V族化合物半导体的PIC如何高效执行AI计算任务。不同于依赖电子分布式神经网络(DNN)的传统AI硬件,光子AI加速器利用光学神经网络(ONN),能以光速运行且能量损耗极低。

Tossoun博士解释道:“硅光子器件虽然易于制造,但难以扩展为复杂集成电路。我们的设备平台可以作为光子加速器的构建模块,其能效和可扩展性远超现有最先进技术。”

该研究团队采用异质集成工艺制造硬件,结合硅光子和III-V族化合物半导体,在功能上集成激光器与光放大器以降低光学损耗并提升可扩展性。III-V族半导体有助于制造更高密度、更复杂的PIC,其支持神经网络所需的全部运算,是下一代AI加速器硬件的理想选择。

制造工艺始于400纳米厚硅层的绝缘体上硅(SOI)晶圆。随后,采用光刻和干法刻蚀工艺对金属氧化物半导体电容(MOSCAP)器件和雪崩光电二极管(APD)进行掺杂。接下来,选择性生长硅和锗形成APD的吸收层、电荷层和倍增层,再采用晶粒到晶圆键合技术将III-V族化合物半导体(如InP或GaAs)集成到硅基平台上。添加薄栅氧化层(Al₂O₃或HfO₂)提升器件效率,最后沉积厚介电层实现封装和热稳定性。

Tossoun博士指出:“这种III-V/SOI异质集成平台为开发AI/ML加速的光子和光电子计算架构提供了所有必要组件,特别适用于采用连续模拟值进行数据表征的模拟ML光子加速器。”

这种独特的光子平台可在单一光子芯片上实现光学神经网络所需各类器件的晶圆级集成,包括片上激光器、放大器等有源器件,高速光电探测器,高能效调制器以及非易失性移相器。这使得基于TONN的加速器的能效比其他光子平台高出2.9×10²倍,比最先进的数字电子器件高出1.4×10²倍。

这项突破性技术将显著降低AI/ML加速的能源成本、提升计算效率,并赋能各领域AI应用发展。展望未来,该技术将使数据中心承载更多AI工作负载,并帮助解决诸多优化问题。该平台将有效应对计算和能源挑战,为构建稳健、可持续的AI加速器硬件奠定基础。

免责声明:本文为转载,非本网原创内容,不代表本网观点。其原创性以及文中陈述文字和内容未经本站证实,对本文以及其中全部或者部分内容、文字的真实性、完整性、及时性本站不作任何保证或承诺,请读者仅作参考,并请自行核实相关内容。

如有疑问请发送邮件至:goldenhorseconnect@gmail.com

- 一天一个西红柿几天就能白 西红柿一天一个什么好处2024-04-26

- 流脑是什么病表现和症状有哪些 流脑疫苗打自费还是免费的?2024-04-26

- 体检发现尿酸高怎么办 需要服药吗为什么?2024-04-26

- 脊柱侧弯是怎么形成的原因是啥 脊柱侧弯正骨能矫正过来吗?2024-04-26

- 脓毒血症是什么病 脓毒血症是怎么引起的一般多久治好?2024-04-26

- 生物胺类物质包括什么 生物胺对人体的影响有哪些2024-04-26

- 手脚血管堵塞最佳治疗方法 感觉手脚血管有点堵塞怎么回事2024-04-26

- 夜尿多就是肾有问题么 夜尿多是肾虚还是前列腺炎?2024-04-26

- 脓毒血症症状表现有哪些 脓毒血症最怕三个征兆2024-04-26

- 淫秽物品认定标准是什么 传播淫秽物品牟利罪如何判定?2024-04-26